- Dapat mensimulasikan Aplikasi informasi gerbang logika

- Dapat mengetahui prinsip kerja pada aplikasi informasi gerbang logika

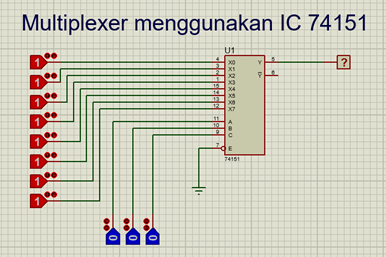

Adalah multiplexer 8-bit dengan delapan input biner (D0 hingga D7), tiga input pilihan (A B dan C) dan input enable (E). IC 74151 menyediakan dua output yaitu Y & Y.

1) Materi Informasi yang Relevan dengan Aplikasi

2) IC 74151

Multiplexer adalah rangkaian logika yang menerima beberapa input data digital dan menyeleksi salah satu dari input tersebut pada saat tertentu, untuk dikeluarkan pada sisi output. Seleksi data-data input dilakukan oleh selector line, yang juga merupakan input dari multiplexer tersebut. Demultiplexer adalah sebuah rangkain logika yang menerima satu input datadan mendistribusikan input tersebut ke beberapa output yang tersedia, dan juga merupakan kebalikkan dari multiplexer. seleksi data - data input dilakukan oleh selektor line, yang juga merupakan input dari demultiplexer tersebut.

Contoh Implementasi Multiplexer Demultiplexer dalam kehidupan sehari-hari:

Multiplexer : Digunakan untuk transmisi jaringan jarak jauh baik yang menggunakan kabel maupun yang menggunakan media udara seperti wireless atau radio. Sebagai contoh satu helai optic bisa dipakai untuk menyalurkan ribuan percakapan pada telepon

Demultiplexer : Digunakan pada televisi karena cara televisi adalah menerima sinyal data yang kemudian akan dipisahkan berdasarkan chanel yang ada cara ini disebut dengan teknik demultiplexing atau lebih jelasnya adalah proses penerimaan data dan kemudian akan dipisahkan sesuai dengan channel yang ada.

Salah satu contoh multiplexer adalah IC 74151. IC 74151 adalah multiplexer 8-bit dengan delapan input biner (D0 hingga D7), tiga input pilihan (A B dan C) dan input enable (E). IC 74151 menyediakan dua output yaitu Y & Y.

2. Pilih komponen yang dibutuhkan, pada rangkaian ini dibutukan sesuai dengan alat dan bahan diatas.

3. Rangkai setiap komponen menjadi rangkaian yang diinginkan.

4. Ubah spesifikasi komponen sesuai kebutuhan.

5. Jalankan simulasi rangkaian.

Output akan berlogika 0 pada saat :

Prinsip kerja

Address CBA bernilai 000 maka output akan logic 0 jika input D0 bernilai 0

Address CBA bernilai 001 maka output akan logic 0 jika input D1 bernilai 0

Address CBA bernilai 010 maka output akan logic 0 jika input D2 bernilai 0

Address CBA bernilai 011 maka output akan logic 0 jika input D3 bernilai 0

Address CBA bernilai 100 maka output akan logic 0 jika input D4 bernilai 0

Address CBA bernilai 101 maka output akan logic 0 jika input D5 bernilai 0

Address CBA bernilai 110 maka output akan logic 0 jika input D6 bernilai 0

Address CBA bernilai 111 maka output akan logic 0 jika input D7 bernilai 0

1. Buatlah Tabel Kebenaran dari Rangkaian Gerbang Logika Berikut Ini

Jawab

2. Buatlah Rangkaian gerbang AND pada proteus

Jawab :

1. Rangkaian dibawah ini merupakan salah satu aplikasi rangkaian IC 74245. Ini adalah Bentuk fisis dari rangakaian apa?

Jawab

Octal 3−State Non-inverting Bus Transceiver

2. Apa yang dimaksud dengan Transceiver ?

Jawab

Transceiver adalah buffer dua arah dengan kontrol arah tambahan dan input ENABLE. ansceiver, seperti buffer, adalah perangkat tristate yang membuatnya kompatibel dengan sistem berorientasi bus.

1.

a. 0

b. 1

c. 2

d. semua benar

Jawaban : a

2.

a.

b.

c.

d.

Jawaban : d